# H8/300 CPU Programming Manual

Ver.-Rev.: 01-03

## **Contents**

# Section 4. CPU

- 4.1 Overview

- 4.2 Programming Model

- 4.3 Addressing Mode

- 4.4 Data Types

- 4.5 Instruction Set

- 4.6 Memory Model

- 4.7 Processing States

- 4.8 CPU Basic Timing

Appendix A. Instruction Set Details

Appendix B. Opcode Map

Appendix C. Instruction Set Summary

## Section 4. CPU

#### 4.1 Overview

The H8/300 has an 8-bit high-speed CPU employing Hitachi's original architecture with RISC type instruction set. The H8/300 CPU has the following features:

- General purpose registers

- Sixteen 8-bit general purpose registers or eight 16-bit general purpose registers

- 53 basic instructions

- Multiplication and division instructions

- Powerful bit manipulation instructions

- Eight addressing modes

- Register direct

- Register indirect

- Register indirect with displacement

- Register indirect with post-increment/ pre-decrement

- Absolute address

- Immediate

- Program counter relative

- Memory indirect

- · High-speed operation

- Most instructions executable in 2 or 4 states

- 16-bit data addition (in general purpose registers) executed in 200 nsec when  $\emptyset = 10$  MHz

- Low power consumption mode instruction

- SLEEP

# 4.2 Programming Model

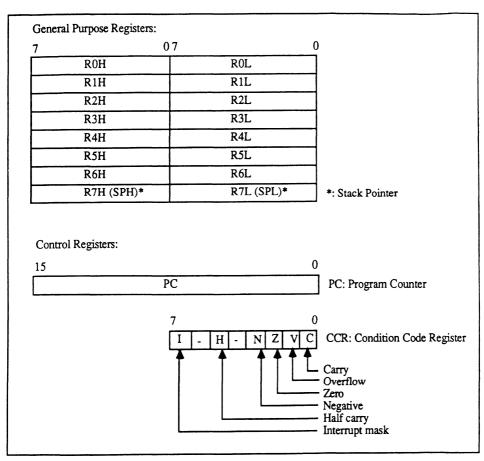

Figure 4-1 shows the H8/300 CPU programming model. The H8/300 has sixteen 8-bit or eight 16-bit general purpose registers, a 16-bit program counter (PC), and an 8-bit condition code register (CCR).

Figure 4-1. H8/300 CPU Programming Model

#### 4.2.1 General Purpose Registers

General purpose registers can be used as either data registers or address registers. When they are used as address registers, they function as 16 bit-registers, while they are used as data registers, they function as either 8 bit-registers or 16 bit-registers depending on op-codes. In addition, general purpose register R7 implicitly functions as the stack pointer for interrupt processing and subroutine calls.

#### 4.2.2 Control Registers

Program Counter (PC): 16-bit PC has the address which points to the next instruction to be executed by the CPU.

Condition Code Register (CCR): 8-bit CCR shows the CPU internal status as described below. CCR, including reserved bits 6 and 4, is accessed by CCR manipulation instructions or transfer instructions. CCR can be used as conditions for branch instruction Bcc. Moreover, CCR is not affected by some instructions. (See Appendix A. Instruction Set Details)

Interrupt mask bit (I): When the I bit is set, interrupts other than NMI are masked.

Half carry flag (H): The H flag is set if a carry or borrow is generated by executing an instruction such as ADD.B, ADDX.B, SUB.B, SUB.X.B, or CMP.B, and cleared otherwise. The H flag is implicitly used for the DAA and DAS instructions. For the ADD.W, SUB.W, and CMP.W instruction, the H flag is set if a carry or borrow occurs from bit 11, and cleared otherwise.

Negative flag (N): The N flag reflects the MSB of result data, which is handled as a sign bit.

Zero flag (Z): The Z flag is set if result data is zero, and cleared otherwise.

Overflow flag (V): The V flag is set if the result overflows, and cleared otherwise.

Carry flag (C): The C flag is set if a carry is generated from MSB by executing an instruction, and cleared otherwise. The C flag also functions as a bit accumulator for bit manipulation instructions. A carry includes the following events:

- A carry generated by addition, shifting, or rotation

- · A borrow generated by subtraction

# 4.2.3 Initial Values of CPU Internal Registers

PC is initialized by reset exception processing since the PC initial value is loaded from the reset vector. However, general purpose registers and CCR\*1 are not initialized by reset exception processing. Register R7 (SP) is also undefined after reset exception processing. Accordingly, general purpose registers including register R7 (SP) must be initialized immediately after reset exception processing.

Note: 1. An exception is that the I bit of CCR is initialized to 1 after reset exception processing.

#### 4.3 Addressing Modes

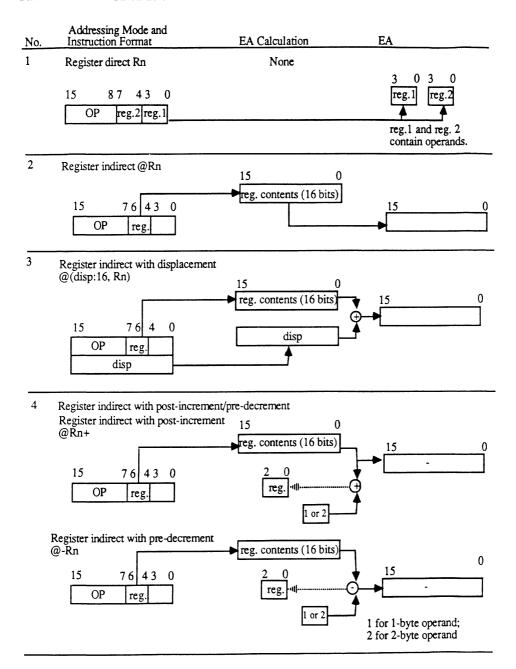

The H8/300 CPU supports eight addressing modes as described below.

#### 4.3.1 Register Direct: Rn

An operand is contained in an 8-bit or 16-bit register specified by the register field in the instruction code. The MOV.W, ADD.W, SUB.W, ADDS.W, SUBS.W, MULXU, and DIVXU instructions use word operands.

#### 4.3.2 Register Indirect: @Rn

An operand address is contained in a 16-bit register specified by the register field in the instruction code.

## 4.3.3 Register Indirect with Displacement: @(disp:16, Rn)

An operand address is calculated by adding a 16-bit displacement contained in the second word (third and forth bytes) of the instruction code to the contents of a 16-bit register specified by the register field in the instruction code. Register indirect with displacement addressing mode is used only for the MOV instruction. For MOV.W, the effective address should be even.

#### 4.3.4 Register Indirect with Post-increment/ Pre-decrement: @Rn+/ @-Rn

Register indirect with post-increment (@Rn+): This addressing mode is used for MOV instruction. An operand address is contained in a 16-bit register specified by the register field in the instruction code. After instruction execution, 1 or 2 is automatically added to the 16-bit register contents: 1 is added for a byte operand, 2 is added for a word (2 bytes) operand. Note that for word operands, the 16-bit register contents must always be even.

Register indirect with pre-decrement (@-Rn): This addressing mode is used for the MOV instruction. An operand address is contained in a 16-bit register specified by the register field in the instruction code. After instruction execution, 1 or 2 is automatically subtracted from the 16-bit register contents: 1 is decremented for a byte operand, 2 is decremented for a word (2 bytes) operand. Note that for word operands, the 16-bit register contents must always be even.

#### 4.3.5 Absolute Address: @aaaa:8/@aaaa:16

An operand address is specified by 8-bit (@aaaa:8) or 16-bit (@aaaa:16) absolute data in the instruction code. 8-bit absolute addressing mode (@aaaa:8) is used for MOV:B, while 16-bit absolute addressing mode (@aaaa:16) is used for MOV.B, MOV.W, JMP, and JSR. In 8-bit absolute addressing mode, the upper 8 bits of the address are all "1"s (FFH); accessible addresses are 65280 through 65535 (FF00H through FFFFH).

#### 4.3.6 Immediate: #XXX:8/#XXX:16

8-bit immediate data in the 2nd byte of the instruction code is used as an operand. For the ADDS.W and SUBS.W instructions, immediate data (1 or 2) is implicitly contained in their instruction codes. In addition, for bit manipulation instructions, 3-bit immediate data is contained in the second or forth byte of their instruction codes.

#### 4.3.7 Program Counter Relative: @(disp:8, PC)

Program counter relative addressing mode is used for the BRA, BRN, Bcc, and BSR instructions. A branch destination address is calculated by adding an 8-bit displacement in the second byte of the instruction code to the PC, which indicates the start address of the next instruction. The 8-bit displacement is sign extended to 16 bits before addition. The allowable offset from the end of the instruction of the branch destination is in the range of -126 to +128 bytes (-63 to +64 words). Note that the displacement and PC must be even.

### 4.3.8 Memory Indirect: @@aaaa:8

Memory indirect addressing mode is used for the JMP and JSR instructions. An operand address is specified by 8-bit absolute data in the second byte of the instruction code. The operand contains a jump destination address. The upper 8 bits of the operand address are all "0"s (00H) so that the accessible address range is 0000H through 00FFH. Note that addresses 0000H through 003DH are also used as vector address space.

Table 4-1 shows how the effective address for each addressing mode is calculated. For arithmetic and logical operation instructions, register direct and immediate addressing modes (only for ADD.B, ADDX.B, SUBX.B, CMP.B, AND.B, OR.B, and XOR.B) can be used. Data transfer instructions can use all addressing modes except for PC relative and memory indirect addressing modes. For bit manipulation instructions, register direct, register indirect, and 8-bit absolute addressing mode can be used. Moreover, for specifying bit number (bit position) in the bit manipulation instructions, register indirect (only for BSET, BCLR, BNOT, and BTST) and 3-bit immediate addressing modes are used.

Table 4-1. EA Calculation

Table 4-1. EA Calculation (cont)

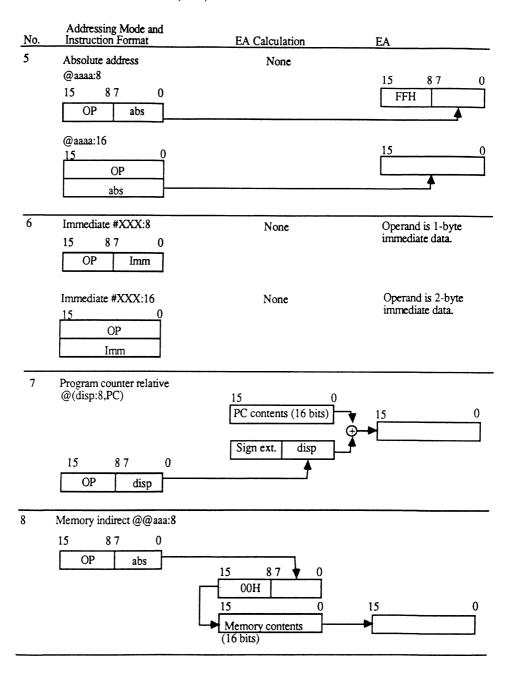

## 4.4 Data Types

The H8/300 CPU supports three data types: 1-bit data, byte data (8 bits), and word data (16 bits). 1-bit data is handled by bit manipulation instructions and is specified by a bit number out of an 8-bit operand. Byte data can be handled by all instructions other than the ADDS and SUBS instructions. Word data is used by the MOV.W, ADD.W, SUB.W, ADDS.W, SUBS.W, MULXU, and DIVXU instructions. In decimal adjust instructions (DAA and DAS), byte data is handled as 2-digit 4-bit BCD data (packed BCD data).

## 4.4.1 Data Organization in General Purpose Registers

Figure 4-2 shows data organization in general purpose registers for the various data types.

Figure 4-2. Data Organization in General Purpose Registers

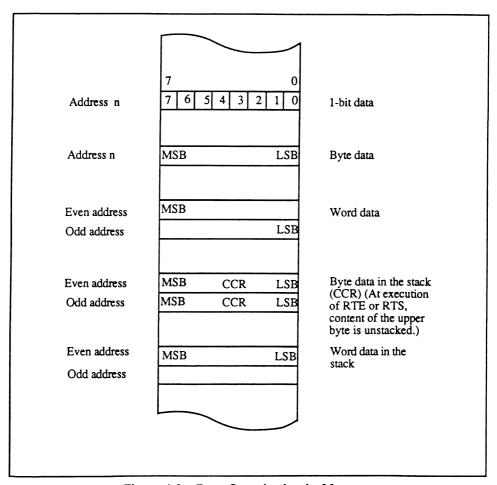

## 4.4.2 Data Organization in Memory

Figure 4-3 shows data organization in memory. The H8/300 CPU can access word (16 bits) data whose upper 8 bits are located at an even address n. However, note that if the upper 8 bits of word data is located at an odd address n, the H8/300 CPU regards the LSB of the address as "0" and accesses word data from address n-1. At this time, an address error does not occur. In addition, the stack must always be accessed on a word basis. When CCR is stacked, the same data of CCR is stacked to the upper byte and the lower.

Figure 4-3. Data Organization in Memory

# 4.5 Instruction Set Summary

The H8/300 CPU has 7 types of instructions as listed below.

Table 4-2. Instruction Types

| No. | Instruction Type       | No. of Instructions |

|-----|------------------------|---------------------|

| 1   | Data transfer          | 1                   |

| 2   | Arithmetic operation   | 13                  |

| 3   | Logical operation      | 3                   |

| 4   | Shift operation        | 8                   |

| 5   | Bit manipulation       | 14                  |

| 6   | Branch operation       | 5                   |

| 7   | System control         | 8                   |

| 8   | EEPROM write operation | 1                   |

|     | Total                  | 53                  |

|     |                        |                     |

# 4.5.1 Data Transfer Instructions

Table 4-3 shows data transfer instructions and functions.

Table 4-3. Data Transfer Instructions

| Instruction | Size | Function                                                                                                                                                                                                                          |

|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOV         | B, W | Rn -> (EA), (EA) -> Rn, #XXX -> Rn  Moves data between general purpose registers, or between a general purpose register and memory, or moves immediate data to a general purpose register.                                        |

|             |      | For word data, Rm, @Rm, @(disp:16, Rm), @aaaa:16, @-Rm, and @Rm+ addressing modes can be used. @aaaa:8 can be used only for byte data. However, note that for @-R7 and @R7+ addressing modes, word data must always be specified. |

| MOVFPE      | В    | @aaaa:16 -> Rn  Moves data from memory to a general purpose register synchronous with the E clock.                                                                                                                                |

| MOVTPE      | В    | Rn -> @aaaa:16  Moves data from a general purpose register to memory synchronous with the E clock.                                                                                                                                |

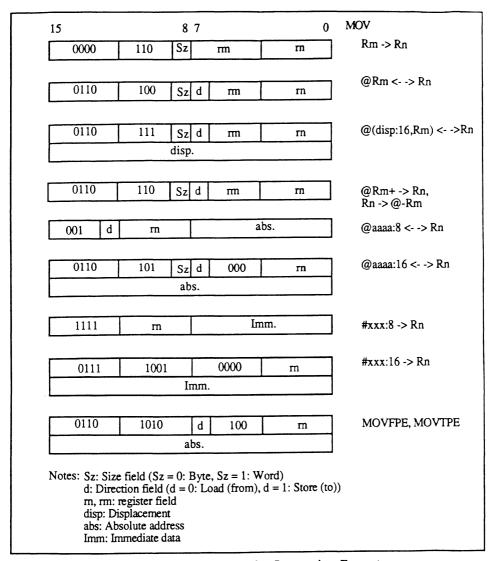

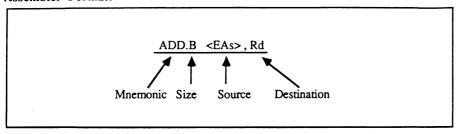

Figure 4-4 shows data transfer instruction format.

Figure 4-4. Data Transfer Instruction Format

# 4.5.2 Arithmtic Operation Instructions

Table 4-4 shows arithmetic operation instructions and functions.

Table 4-4. Arithmetic Operation Instructions

| Instruction Size |   | Function                                                                      |  |  |  |

|------------------|---|-------------------------------------------------------------------------------|--|--|--|

| ADD B, W         |   | Rn ± Rm -> Rn, Rn + #XXX -> Rn                                                |  |  |  |

| SUB              |   | Performs addition or subtraction between general purpose                      |  |  |  |

|                  |   | registers, or addition between a general purpose register and                 |  |  |  |

|                  |   | immediate data. Note that subtraction between immediate data and              |  |  |  |

|                  |   | a general purpose register cannot be performed.                               |  |  |  |

|                  |   | Word data can be handled in addition or subtraction between                   |  |  |  |

|                  |   | general purpose registers.                                                    |  |  |  |

| ADDX             | В | $Rn \pm Rm \pm C \rightarrow Rn, Rn \pm #XXX + C \rightarrow Rn$              |  |  |  |

| SUBX             |   | Performs addition or subtraction with carry between general                   |  |  |  |

|                  |   | purpose registers or between a general purpose register and immediate data.   |  |  |  |

| INC              | В | Rn ± #1 -> Rn                                                                 |  |  |  |

| DEC              |   | Increments or decrements a general purpose register by 1.                     |  |  |  |

| ADDS             | W | Rn ± #XXX -> Rn                                                               |  |  |  |

| SUBS             |   | Performs addition or subtraction between immediate data ("1" or               |  |  |  |

|                  |   | "2") and a general purpose register.                                          |  |  |  |

| DAA              | В | Rn (Decimal Adjustment) -> Rn                                                 |  |  |  |

| DAS              |   | Performs decimal adjustment on general purpose register data                  |  |  |  |

|                  |   | according to the CCR after arithmetic operation and produces                  |  |  |  |

|                  |   | packed BCD data.                                                              |  |  |  |

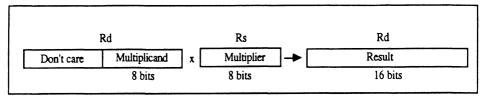

| MULXU            | В | Rn x Rm -> Rn                                                                 |  |  |  |

|                  |   | Multiplies 8-bit general purpose register data with 8-bit general             |  |  |  |

|                  |   | purpose register data. Multiplication is performed using unsigned arithmetic. |  |  |  |

Table 4-4. Arithmetic Operation Instructions (cont)

| Instruction | Size | Function                                                                                                                                                                                                                                |

|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

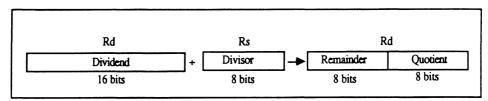

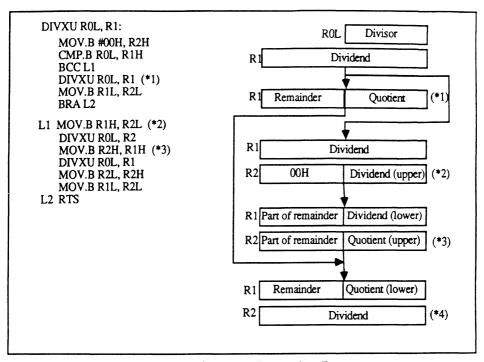

| DIVXU       | D    | Rn + Rm -> Rn  Divides 16-bit general purpose register data by 8-bit general purpose register data.                                                                                                                                     |

| CMP         | B, W | Rn - Rm, Rn - #XXX  Compares data in general purpose registers, or compares data in a general purpose register with immediate data. Word data is used only at comparison of the general purpose register with general purpose register. |

| NEG         | В    | 0 - Rn -> Rn  Takes two's complement of general purpose register data.                                                                                                                                                                  |

# 4.5.3 Logical Operation Instructions

Table 4-5 shows logical operation instructions and functions.

Table 4-5. Logical Operation Instructions

| Instruction | Size | Function                                                            |

|-------------|------|---------------------------------------------------------------------|

| AND         | В    | Rn ^ Rm -> Rn, Rn ^ #XXX -> Rn                                      |

|             |      | Performs logical AND operation between general purpose registers    |

|             |      | or between general purpose register and immediate data.             |

| OR          | В    | Rn v Rm -> Rn, Rn v #XXX -> Rn                                      |

|             |      | Performs logical OR operation between general purpose registers     |

|             |      | or between a general purpose register and immediate data.           |

| XOR         | В    | Rn + Rm -> Rn, Rn + #XXX -> Rn                                      |

|             |      | Performs exclusive OR operation between general purpose             |

|             |      | registers or between a general purpose register and immediate data. |

| NOT         | В    | ~Rn -> Rn                                                           |

|             |      | Takes one's complement of a general purpose register.               |

|             |      |                                                                     |

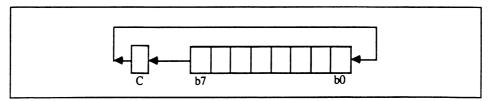

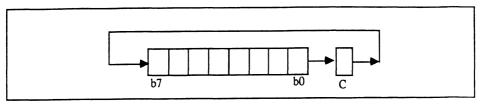

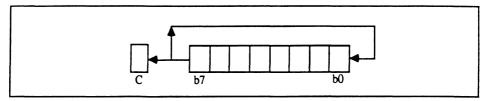

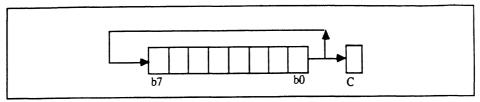

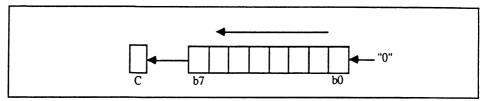

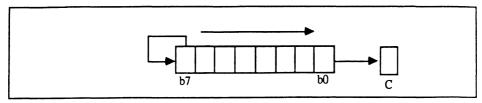

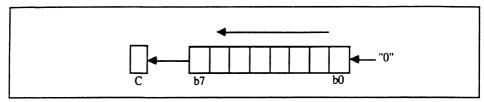

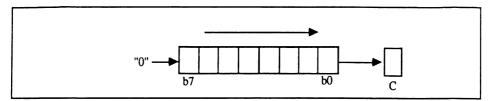

## 4.5.4 Shift Instructions

Table 4-6 shows shift instructions and functions.

Table 4-6. Shift Instructions

| Instruction    | Size | Function                                                                       |

|----------------|------|--------------------------------------------------------------------------------|

| SHAL,<br>SHAR  | В    | Rn (shift operation) -> Rn Arithmetically shifts general purpose register data |

| SHLL<br>SHLR   | В    | Rn (shift operation) -> Rn  Logically shifts general purpose register data     |

| ROTL           | В    | Rn rotate operation -> Rn Rotates general purpose register data                |

| ROTXL<br>ROTXR | В    | Rn rotate operation -> Rn Rotates general purpose register with C flag         |

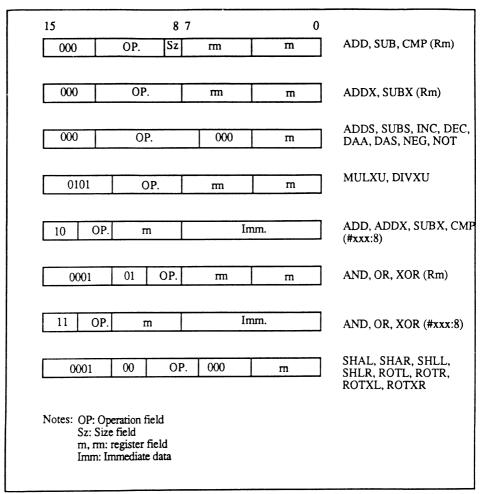

Figure 4-5 shows the instruction format of arithmetic and logical operation instructions, and shift instructions.

Figure 4-5. Arithmetic/Logical Operation Instruction and Shift Instruction Formats

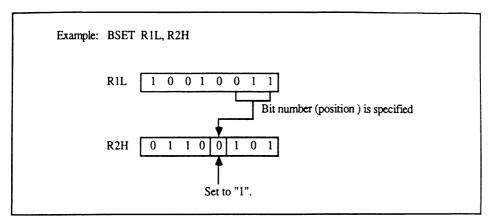

# 4.5.5 Bit Manipulation Instructions

Table 4-7 shows bit manipulation instructions and functions.

Table 4-7. Bit Manipulation Instructions

| Instruction   | Size | Function                                                                                                                                                                                                                                                                                                                                                           |

|---------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BSET          | В    | 1 -> Bit of (EA)  Sets a bit within the operand located in a general purpose register or memory. The bit number is specified by immediate data or a general purpose register.                                                                                                                                                                                      |

| BCLR          | В    | 0 -> Bit of (EA)  Clears a bit within the operand located in a general purpose register or memory. The bit number is specified by immediate data or a general purpose register.                                                                                                                                                                                    |

| BNOT          | В    | ~Bit of (EA) -> Bit of (EA)  Inverts a bit of an operand in a general purpose register or memory. The bit number is specified by immediate data or a general purpose register.                                                                                                                                                                                     |

| BTST          | В    | ~Bit of (EA) -> Z  Tests a bit within the operand located in a general purpose register or memory and set the Z flag according to the result. The bit number is specified by immediate data or a general purpose register.                                                                                                                                         |

| BAND<br>BIAND | В    | C \( Bit of (EA) -> C, C \( \sigma \) RBit of (EA) -> C,  Performs logical AND operation between the C bit and a bit within the operand located in a general purpose register or memory (EA), or first inverts a bit of the operand before performing logical AND operation between the C bit and the inverted bit. The bit number is specified by immediate data. |

Table 4-7. Bit Manipulation Instructions (cont)

| Instruction   | Size                                                                                                                                   | Function                                                                                                                                                                                                                                                                                                                                              |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BOR<br>BIOR   | Performs logical OR operation between the operand located in a general purpose registe first inverts a bit of the operand and then per | C v Bit of (EA) -> C, C v ~Bit of (EA) -> C,  Performs logical OR operation between the C bit and a bit of the operand located in a general purpose register or memory (EA), or first inverts a bit of the operand and then perform logical OR operation between the C bit and the inverted bit. The bit number is specified by immediate data.       |

| BXOR<br>BIXOR | В                                                                                                                                      | C ++ Bit of (EA) -> C, C ++ ~Bit of (EA) -> C,  Performs exclusive OR operation between the C bit and a bit of the operand located in a general purpose register or memory (EA), or first inverts a bit of the operand and then perform exclusive OR operation between the C bit and the inverted bit. The bit number is specified by immediate data. |

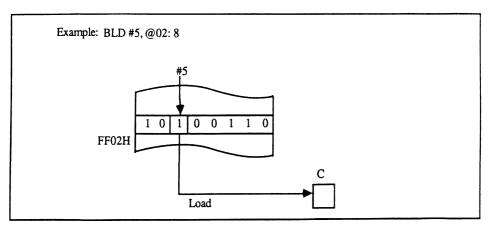

| BLD<br>BILD   | В                                                                                                                                      | Bit of (EA) -> C, ~Bit of (EA) -> C  Loads a bit of the operand located in a general purpose register or memory (EA) into the C flag, or first inverts a bit of the operand and then loads the inverted bit into the C flag. The bit number is specified by immediate data.                                                                           |

| BST<br>BIST   | В                                                                                                                                      | C -> Bit of (EA), ~C -> Bit of (EA)  Stores the C flag into a bit of the operand located in a general register or memory (EA), or first inverts the C flag and then stores the inverted C flag into a bit of the operand.  The bit number is specified by immediate data.                                                                             |

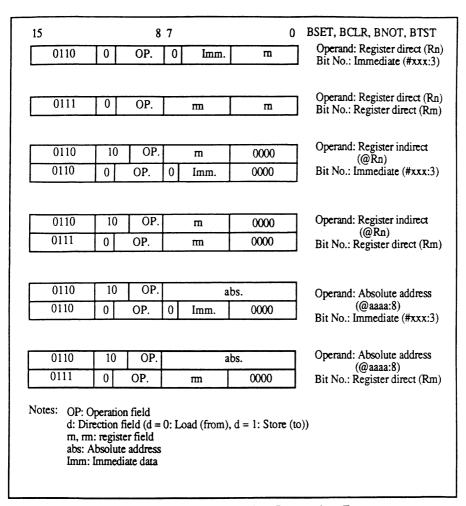

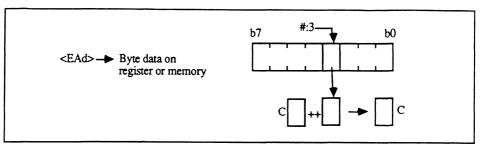

Figure 4-6 shows bit manipulation instruction formats.

Figure 4-6. Bit Manipulation Instruction Formats

| 15                         | 8                                                                                             | 7              | (                | ,,,,,,,,,,,,                                              |

|----------------------------|-----------------------------------------------------------------------------------------------|----------------|------------------|-----------------------------------------------------------|

| 011 d                      | 011 d 0 OP.                                                                                   |                | m                | Operand: Register direct (Rn) Bit No.: Immediate (#xxx:3) |

|                            |                                                                                               |                |                  | = = = = = = = = = = = = = = = = = = =                     |

| 0110                       | 10 OP.                                                                                        | l rn           | 0000             | Operand: Register indirect                                |

| 011 d                      |                                                                                               | 0 Imm.         | 0000             | (@Rn) Bit No.: Immediate (#xxx:3)                         |

| <u> </u>                   | <del></del>                                                                                   | I I            | I                | J                                                         |

| 0110                       | 10 OP.                                                                                        | a              | bs.              | Operand: Absolute address (@aaaa:8)                       |

| 011 d                      | 0 OP.                                                                                         | 0 Imm.         | 0000             | Bit No.: Immediate (#xxx:3)                               |

|                            |                                                                                               |                | •                |                                                           |

|                            |                                                                                               |                |                  | BIAND, BIOR, BIXOR, BILD,<br>BTST                         |

| 011 d                      | 0 OP.                                                                                         | 1 Imm.         | m                | Operand: Register direct (Rn) Bit No.: Immediate (#xxx;3) |

| <u> </u>                   | <del></del>                                                                                   | L              |                  | J Dit 140 Hillinediate (#XXX.3)                           |

| 0110                       | 10 OP.                                                                                        | T              |                  | Operand: Register indirect                                |

| 0110<br>011 d              | 10 OP.                                                                                        | m<br>1 Imm.    | 0000             | (@Rn) Bit No.: Immediate (#xxx:3)                         |

| 011   4                    | OF.                                                                                           | 1 1111111.     | 0000             | Die Tvoir Mandelade (Wickels)                             |

| 0110                       | 10 OP.                                                                                        |                |                  | Operand: Absolute address                                 |

| 0110<br>011 d              | 0 OP.                                                                                         | 1 Imm.         | bs. 0000         | (@aaaa:8) Bit No.: Immediate (#xxx:3)                     |

| 011 12                     | 01.                                                                                           |                | 0000             | , , ,                                                     |

| d: Dir<br>rn, rm<br>abs: A | peration field<br>ection field (d =<br>: register field<br>.bsolute address<br>Immediate data | 0: Load (from) | , d = 1: Store ( | to))                                                      |

Figure 4-6. Bit Manipulation Instruction Formats (cont)

## 4.5.6 Branch Instructions

Table 4-8 shows branch instructions and functions.

Table 4-8. Branch Instructions

| Instruction | Size | Function                                                                  |          |                            |                       |  |

|-------------|------|---------------------------------------------------------------------------|----------|----------------------------|-----------------------|--|

| Bcc         | -    | Branches to a specified address if the condition specified in cc is true. |          |                            |                       |  |

|             |      | Mnemonic                                                                  | cc       | Condition                  | Test                  |  |

|             |      | BRA (BT)                                                                  | 0000     | Always (True)              | 1                     |  |

|             |      | BRN (BF)                                                                  | 0001     | Never (False)              | 0                     |  |

|             |      | ВНІ                                                                       | 0010     | High                       | ~(C + Z)              |  |

|             |      | BLS                                                                       | 0011     | Low or Same                | C + Z                 |  |

|             |      | BCC (BHS)                                                                 | 0100     | Carry Clear (High or Same) | ) ~C                  |  |

|             |      | BCS (BLO)                                                                 | 0101     | Carry Set (Low)            | С                     |  |

|             |      | BNE                                                                       | 0110     | Not Equal                  | ~Z                    |  |

|             |      | BEQ                                                                       | 0111     | Equal                      | Z                     |  |

|             |      | BVC                                                                       | 1000     | Overflow Clear             | ~V                    |  |

|             |      | BVS                                                                       | 1001     | Overflow Set               | V                     |  |

|             |      | BPL                                                                       | 1010     | Plus                       | ~N                    |  |

|             |      | BMI                                                                       | 1011     | Minus                      | N                     |  |

|             |      | BGE                                                                       | 1100     | Greater Than or Equal      | ~(N ++ V)             |  |

|             |      | BLT                                                                       | 1101     | Less Than                  | N + V                 |  |

|             |      | BGT                                                                       | 1110     | Greater Than               | $\sim (Z + (N ++ V))$ |  |

|             |      | BLE                                                                       | 1111     | Less Than or Equal         | Z + (N ++ V)          |  |

| IMP         | -    | Always jumps                                                              | to a spe | cified address             |                       |  |

| BSR<br>ISR  | -    | Branches to a                                                             | subrouti | ne at a specified address. |                       |  |

| RTS         | -    | Returns from                                                              | a subrou | tine.                      |                       |  |

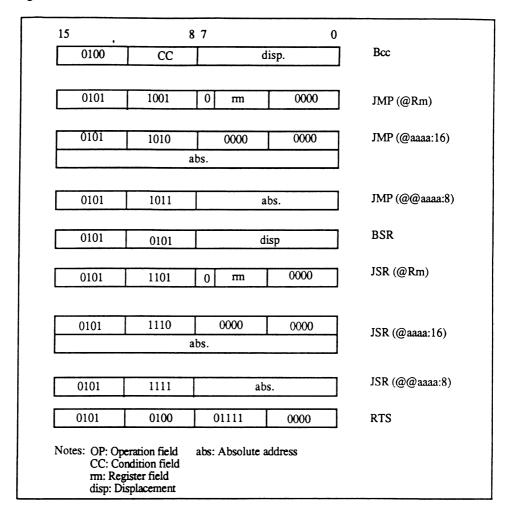

Figure 4-7 shows branch instruction formats.

Figure 4-7. Branch Instruction Formats

# 4.5.7 System Control Instructions

Table 4-9 shows system control instructions and functions.

Table 4-9. System Control Instructions

| Instruction | Size | Function                                                            |  |  |  |

|-------------|------|---------------------------------------------------------------------|--|--|--|

| RTE         | -    | Returns from an interrupt service routine.                          |  |  |  |

| SLEEP       | -    | Enters sleep mode and waits for interrupt generation.               |  |  |  |

| LDC         | В    | Rn -> CCR, #XXX -> CCR                                              |  |  |  |

|             |      | Loads general purpose register data or immediate data into the CCR. |  |  |  |

| STC         | В    | CCR -> Rn                                                           |  |  |  |

|             |      | Stores the CCR in a general purpose register.                       |  |  |  |

| ANDC        | В    | CCR ∧ #XXX -> CCR                                                   |  |  |  |

|             |      | Performs a logical AND operation between the CCR and                |  |  |  |

|             |      | immediate data.                                                     |  |  |  |

| ORC         | В    | CCR V #XXX -> CCR                                                   |  |  |  |

|             |      | Performs a logical OR operation between the CCR and immediate       |  |  |  |

|             |      | data.                                                               |  |  |  |

| XORC        | В    | CCR ++ #XXX -> CCR                                                  |  |  |  |

|             |      | Performs an exclusive OR operation between the CCR and              |  |  |  |

|             |      | immediate data.                                                     |  |  |  |

| NOP         | -    | Performs no operation. Only PC is incremented.                      |  |  |  |

|             |      |                                                                     |  |  |  |

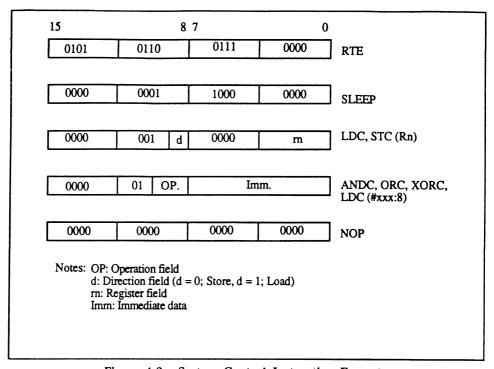

Figure 4-8 shows the system control instruction formats.

Figure 4-8. System Control Instruction Formats

## 4.5.8 EEPROM Write Instruction

Table 4-10 shows the EEPROM write instruction and function.

Table 4-10. EEPROM Write Instruction

| Size | Function                                                                                                                                                                                                                                                                                                                    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| В    | @R5+->@R6+ EEPMOV is a dedicated EEPROM write instruction.  Data in memory, whose start address is specified by R5 and whose byte size is specified by R4L, is loaded to EEPROM whose start address is specified by R6. The next instruction can be executed after the data has been loaded and EEPROM write has completed. |

|      |                                                                                                                                                                                                                                                                                                                             |

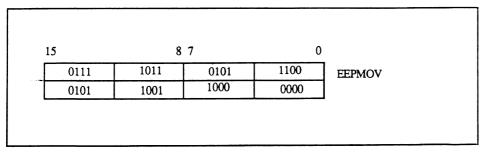

Figure 4-9 shows the EEPROM instruction format.

Figure 4-9. EEPMOV Instruction Format

- \*1. The EEPMOV instruction acts as a simple block data transfer instruction when MCU has no EEPROM.

- \*2. The next instruction can be executed immediately after the transfer completion.

# 4.6 Memory Model

The H8/300 CPU can support a maximum of 64 K bytes of memory space which can be used for program code and data storage areas.

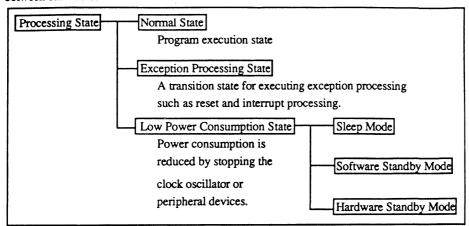

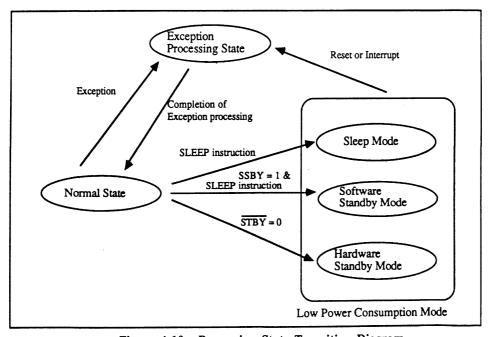

#### 4.7 Processing States

The H8/300 CPU has three processing states: normal state, exception processing state, and low power consumption state as shown in Figure 4-9. Figure 4-10 shows the transition diagram between each state.

Figure 4-9. Processing States

Figure 4-10. Processing State Transition Diagram

#### 4.7.1 Normal State

In normal state, the H8/300 CPU executes a program sequentially. Normal state has two modes: normal and interrupt modes, in which usable resources are almost the same. Branching to or returning from a subroutine is achieved by referring to the stack pointer (SP:R7) and the program counter (PC).

#### 4.7.2 Exception Processing State

Exception processing state is a transition state before reset or interrupt processing begins. All interrupts other than reset pushes the PC and CCR onto the stack according to the SP.

#### 4.7.3 Low Power Consumption State

Sleep Mode: Sleep mode is entered by executing the SLEEP instruction; the CPU halts operation just after the SLEEP instruction and the CPU internal status is retained. Sleep mode is cancelled by reset or an interrupt. If a reset or interrupt exception occurs, the CPU enters normal state via exception processing state.

Software Standby Mode: Software standby mode is entered by executing the SLEEP instruction after the SSBY bit of SBYCR has been set. In software standby mode, the CPU and all on-chip peripheral devices halt operation. However, the CPU internal status and internal RAM are retained.

Hardware Standby Mode: Hardware standby mode is entered by bringing the STBY pin to low. In this mode, CPU and all on-chip peripheral devices halt operation.

See "6. Low Power Consumption Mode" for details.

## 4.8 CPU Basic Timing

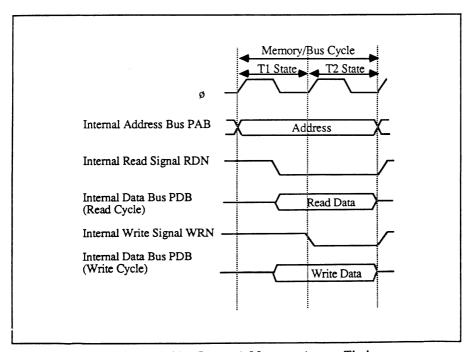

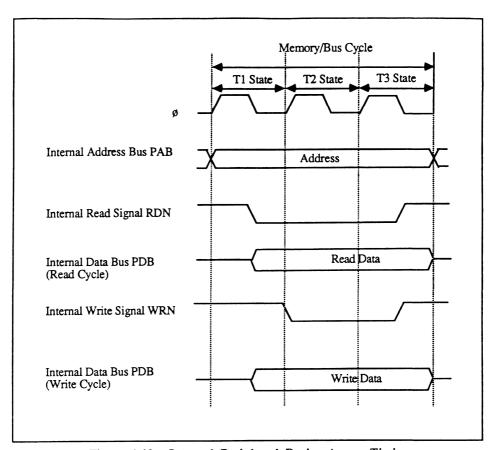

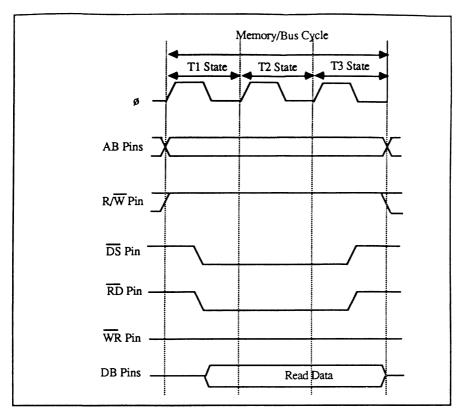

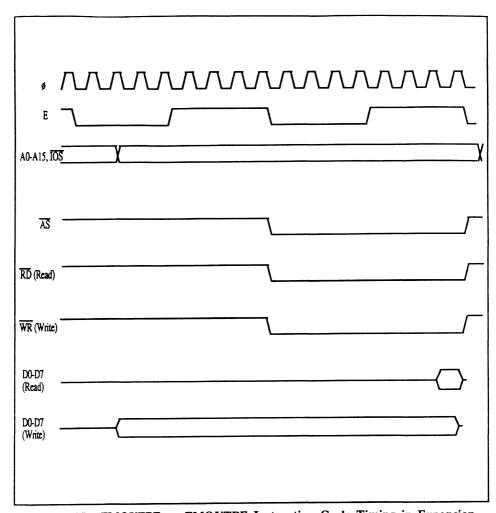

The H8/300 CPU operates based on the ø clock, in which one rising edge to the next rising edge period is called a state. A memory cycle or bus cycle is normally comprised of 2 or 3 states. On-chip memory, internal peripheral device, and external device access timings are shown below.

#### 4.8.1 On-chip Memory (RAM, ROM, and EEPROM) Access Timing

On-chip memory is accessed in 2 states. A 16-bit data bus enables byte or word size access. Figure 4-11 shows on-chip memory access timing.

#### 4.8.2 Internal Peripheral Devices/External Devices Access Timing

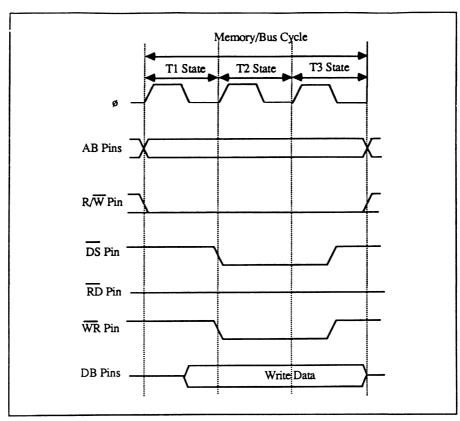

Internal peripheral devices and external devices are accessed in 3 states by using an 8-bit data bus. Word data and word instruction code are accessed in two groups of one-byte each. Figures 4-11 and 4-12 show internal memory and peripheral device access timings, respectively. Figures 4-13 and 4-14 show external devices access timings.

Figure 4-11. Internal Memory Access Timing

Figure 4-12. Internal Peripheral Device Access Timing

Figure 4-13. External Device Access Timing (Read Cycle)

Figure 4-14 External Device Access Timing (Write Cycle)

## 4.9 6800 Family Bus Interface

The H8/300 CPU provides two transfer instructions synchronous with E clock (MOVFPE and MOVTPE) and an E clock pin to facilitate 6800 family bus interface in expansion modes. The E clock is produced by dividing ø clock by eight and can be output when the DDR0 pin of port 8 is set to 1 (After reset, E clock is output.).

When the CPU executes the MOVFPE or MOVFTPE instruction, address bus, IOOE and data bus are output in the same timing as in normal access. However, DS, RD, and WR are asserted after the falling edge of the E clock is detected as shown in Figures 4-15 and 4-16. In addition, MOVFPE and MOVTPE execution cycles are 8-15 states and cannot be fixed. Moreover, Tw state by the WAIT pin cannot be inserted during MOVFPE and MOVTPE instruction cycles.

When interfacing the H8/300 CPU and a 6800 family peripheral device, the WR pin of the H8/300 CPU must be connected to the R/W pin of the 6800 family peripheral device. All pins other than WR can be connected in the same way as in normal peripheral device interface. Needless to say, the system must be designed so that all peripheral device timing specifications are satisfied.

Figure 4-15. FMOVFPE or FMOVTPE Instruction Cycle Timing in Expansion Mode (Maximum Synchronization)

# Appendix A. Instruction Set Details

This section describes the H8/300 CPU instruction set.

# A-1. Instruction Set Description

Items used in the instruction set details are outlined below.

#### Assembler Format:

Byte (B) and/or word (W) operand can be selected in the size field according to the instruction. In addition, the size field can be omitted for an instruction whose operand size is fixed to byte (B) or word (W).

<EA> indicates that multiple addressing modes can be specified in the EA field. The H8/300 CPU supports the addressing modes listed below.

| Symbol         | Addressing Mode                                        |

|----------------|--------------------------------------------------------|

| R              | Register direct                                        |

| @R             | Register indirect                                      |

| @(disp:16, R)  | Register indirect with displacement                    |

| @R+, @-R       | Register indirect with post-increment or pre-decrement |

| @aaaa:8/16     | Absolute address (8 or 16 bits)                        |

| #XXX:3/8/16    | Immediate (3, 8 or 16 bits)                            |

| @(disp: 8, PC) | Program counter relative                               |

| @@aaaa:8       | memory indirect                                        |

Operation: Symbols used in the operation field is listed below.

| Symbol     | Description                                                 |

|------------|-------------------------------------------------------------|

| PC         | Program counter                                             |

| SP         | Stack pointer (R7)                                          |

| CCR        | Condition code register                                     |

| Z          | Zero flag in CCR                                            |

| C          | Carry flag in CCR                                           |

| Rs, Rd, Rn | General purpose register (8-bit: R0H-R7L or 16 bits: R0-R7) |

| disp       | Displacement                                                |

| ->         | Direction of operand transfer or status transition          |

| +          | Addition                                                    |

| -          | Subtraction                                                 |

| x          | Multiplication                                              |

| +          | Division                                                    |

| ^          | Logical AND                                                 |

| <u>v</u>   | Logical OR                                                  |

| ++         | Exclusive OR                                                |

| ~          | One's complement                                            |

| () or <>   | Contents of effective address                               |

Condition Code: Symbols used in condition codes are listed below.

| Symbol | Description                                                                     |

|--------|---------------------------------------------------------------------------------|

| S      | Set normally, that is:                                                          |

|        | I: Set if an interrupt is masked, cleared otherwise.                            |

|        | H: Set if carry or borrow is generated from bit 3 or bit 11, cleared otherwise. |

|        | N: Set if result is negative, cleared otherwise.                                |

|        | Z: Set if result is zero, cleared otherwise.                                    |

|        | V: Set if result overflows, cleared otherwise.                                  |

|        | C: Set if carry or borrow is generated from bit 7 or bit 15, cleared othewise.  |

| S*     | See explanation                                                                 |

| 0      | Cleared to 0                                                                    |

| 1      | Set to 1                                                                        |

| *      | Undefined                                                                       |

| U      | Unaffected                                                                      |

Instruction Format: Symbols used in the instruction format is listed below.

| Symbol     | Description                                                                                                                                                                           |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Imm        | Immediate data (3, 8 or 16 bits)                                                                                                                                                      |

| abs        | Absolute address (8 or 16 bits)                                                                                                                                                       |

| disp       | Displacement (8 or 16 bits)                                                                                                                                                           |

| rs, rd, rn | Register number (3 or 4 bits).  rs corresponds to Rs and @Rs addressing modes, rd corresponds to Rd and @Rd addressing modes, and rn corresponds to Rn addressing mode, respectively. |

When rs, rd, and rn are used as an address register for @R, @(disp:16, R), @-R, or @R+ addressing mode, they function as 16-bit registers specified by the 3-bit register field as shown below.

On the other hand, when rs, rd, and rn are used as a data register, they function as either a 16-bit register specified by a 3-bit register field for word data or 8-bit register specified by 4-bit register field for byte data. In the 4-bit register field, the lower 3 bits specify the register number and the MSB specifies the upper or lower byte of the register.

| 16-bit Register Specification: |          | 8-bit Register | Specification: |

|--------------------------------|----------|----------------|----------------|

| 3-bit r Field                  | Register | 4-bit r Field  | Register       |

| 000                            | R0       | 0000           | R0H            |

| 001                            | R1       | 0001           | R1H            |

| :                              | :        | :              | :              |

| :                              | :        | :              | :              |

| 111                            | R7       | 0111           | R7H            |

|                                |          | 1000           | ROL            |

|                                |          | 1001           | R1L            |

|                                |          | :              | :              |

|                                |          | :              | :              |

1111

R7L

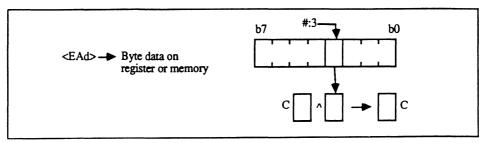

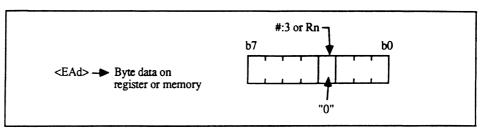

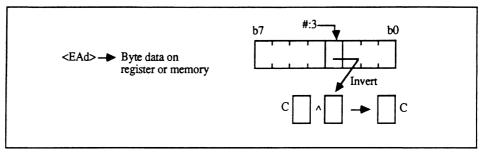

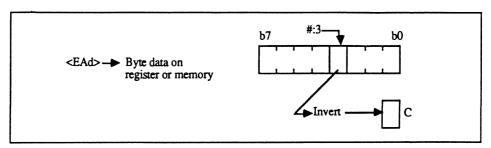

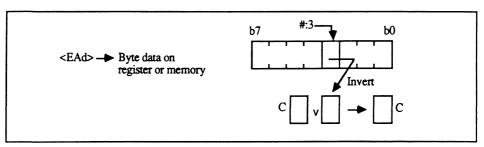

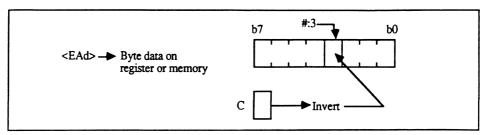

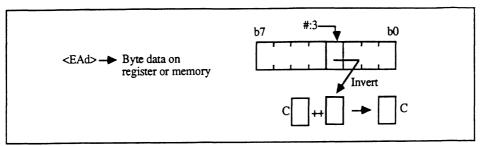

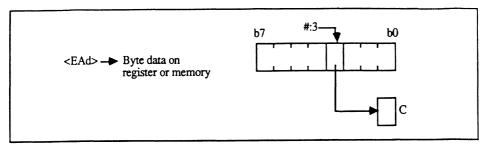

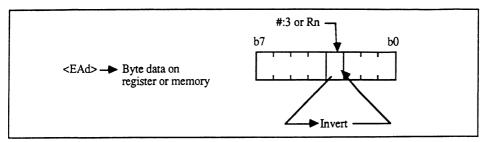

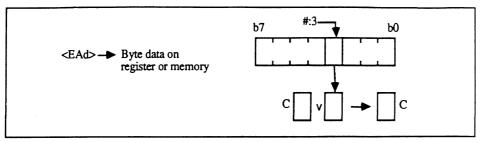

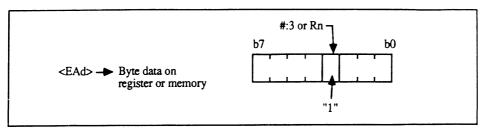

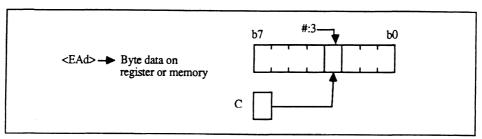

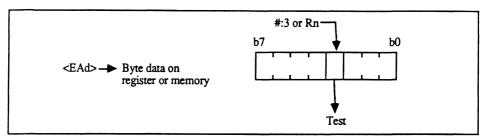

Bit Data Access in Bit Manipulation Instructions: Bit data can be accessed as the n-th bit (n = 0 to 7) of a byte operand in register or memory. The bit number n is specified by 3-bit immediate data or the lower 3 bits of a general purpose register. Examples, whose addressing mode are register or memory, are shown below.

Figure A-1. Bit Data Access in Bit Manipulation Instruction 1

Figure A-2. Bit Data Access in Bit Manipulation Instruction 2

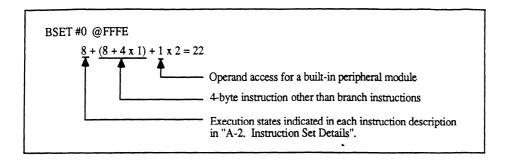

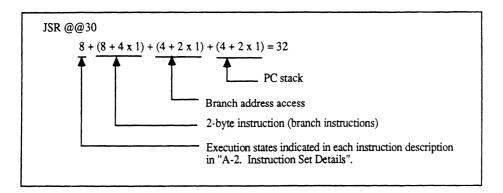

Execution States: Execution states indicates the number of execution states when the instruction and operand are stored in internal memory. When the instruction or operand is stored in area other than internal memory area, the number of execution states increases as shown below.

| Access C    | ondition                      |                           | Number of Increased<br>Execution States |         |  |

|-------------|-------------------------------|---------------------------|-----------------------------------------|---------|--|

| Operand     |                               | On-chip periphera devices | l Byte data                             | 1       |  |

|             |                               |                           | Word data                               | 4       |  |

|             |                               | External device           | Byte data                               | 1 + m   |  |

|             |                               |                           | Word data                               | 4 + 2m  |  |

| Instruction | Instruction other than branch | External memory           | 2-byte instruction                      | 4 + 2m  |  |

|             | instruction                   |                           | 4-byte instruction                      | 8 + 4m  |  |

|             | Branch instruction            |                           | 2-byte instruction                      | 8 + 4m  |  |

|             |                               |                           | 4-byte instruction                      | 12 + 6m |  |

|             |                               |                           |                                         |         |  |

Notes: 1. m = number of Tw states that might be inserted in external device access cycle

- 2. Operand data is accessed twice in BSET, BCLR, BNOT, BST, BIST instructions.

- 3. In memory indirect addressing mode (@@aaaa:8), (4 + 2m) states should be added for word operand access (branch address access) in mode 1.

- 4. If the stack is located in an external device, (4 + 2m) states should be added for BSR, JSR, and RTS instruction cycles since BSR, JSR, and RTS performs word operand access for PC pushing or popping.

5. RTE performes word operand twice for CCR and PC popping. Accordingly, if the stack is located in an external device, (8 + 4m) states should be added.

Examples: When the stack is located in an external device and one Tw state is inserted for an external device access cycle in mode 1

- 6. If R4L is specified as n in the EEPMOV instruction, source and destination operands are accessed (n + 1) times each.

- 7. \*1 = not added for MOVFE and MOVTPE

### A-2. Instruction Set Details

## A.2.1 ADD (Add Binary)

Assembler Format: ADD.B <EAs>, Rd

Operation: (Destination) + (Source) -> Destination

Description: Adds the source operand to the destination operand, and loads the result to the

destination.

Operand Size: Byte

#### Condition Codes:

## Operand Format and Number of Execution States:

#### Instruction Format

| Addressing<br>Mode | Mnemonic | Operand<br>Format | 1st | Byte | 2nd | Byte | 3rd Byte | 4th Byte | Exec.<br>States |

|--------------------|----------|-------------------|-----|------|-----|------|----------|----------|-----------------|

| Immediate          | ADD.B    | #:8, Rd           | 8   | rd   | Iı  | nm   |          |          | 2               |

| Register direct    | ADD.B    | Rs, Rd            | 0   | 8    | rs  | rd   |          |          | 2               |

Notes:

## A.2.2 ADD (Add Binary)

Assembler Format: ADD.W Rs, Rd

Operation: (Destination) + (Source) -> (Destination)

Description: Adds the source operand to the destination operand, and loads the result to the

destination.

Operand Size: Word

Condition Codes:

Operand Format and Number of Execution States:

## **Instruction Format**

| Addressing<br>Mode | Mnemonic | Operand<br>Format | 1st | Byte | 2nd  | Byte 3rd Byte 4 | th Byte | Exec.<br>States |

|--------------------|----------|-------------------|-----|------|------|-----------------|---------|-----------------|

| Register direct    | ADD.W    | Rs, Rd            | 0   | 9    | 0 rs | 0 rd            |         | 2               |

Notes:

## A.2.3 ADDX (Add with Extended Carry)

Assembler Format: ADDX.B <EAs>, Rd

Operation: (Destination) + (Source) + C -> (Destination)

Description: Adds the source operand to destination operand with C flag, and loads the result

to the destination.

Operand Size: Byte

Condition Codes:

S\*: unchanged if result is zero, cleared to 0 otherwise.

Operand Format and Number of Execution States:

#### **Instruction Format**

| Addressing<br>Mode | Mnemonic | Operand<br>Format | 1st | Byte | 2nd Byte | 3rd Byte 4th Byt | Exec.<br>e States |

|--------------------|----------|-------------------|-----|------|----------|------------------|-------------------|

| Immediate          | ADDX.B   | #:8, Rd           | 9   | rd   | Imm      |                  | 2                 |

| Register direct    | ADDX.B   | Rs, Rd            | 0   | Е    | rs rd    |                  | 2                 |

Notes: None

#### A.2.4 ADDS (Add with Sign Extension)

Assembler Format: ADDS.W #1, Rd

ADDS.W #2, Rd

Operation: (Destination) + 1 -> (Destination)

(Destination) +2 -> (Destination)

Description: Adds immediate data "1" or "2" to destination operand, and loads the result to the

destination. ADDS execution does not affect condition codes.

Operand Size: Word

Condition Codes:

Operand Format and Number of Execution States:

### Instruction Format

| Addressing<br>Mode | Mnemonic | Operand<br>Format | 1st | Byte | 2nd | Byte 3rd | Byte 4th | Exec.<br>Byte States |

|--------------------|----------|-------------------|-----|------|-----|----------|----------|----------------------|

| Register direct    | ADDS.W   | #1, Rd            | 0   | В    | 0   | 0 rd     |          | 2                    |

| Register direct    | ADDS.W   | #2, Rd            | 0   | В    | 8   | 0 rd     |          | 2                    |

Notes: ADDS cannot handle byte data.

## A.2.5 AND (AND Logical)

Assembler Format: AND.B <EAs>, Rd

Operation: (Destination) A (Source) -> (Destination)

Description: Performs a logical AND operation between the source operand and destination

operand, and loads the result to the destination.

Operand Size: Byte

Condition Codes:

## Operand Format and Number of Execution States:

#### **Instruction Format**

| Addressing<br>Mode | Mnemonic | Operand<br>Format | 1st | Byte | 2nd Byte 3 | rd Byte 4th | Exec.<br>Byte States |

|--------------------|----------|-------------------|-----|------|------------|-------------|----------------------|

| Immediate          | AND.B    | #:8, Rd           | Е   | rd   | Imm        |             | 2                    |

| Register direct    | AND.B    | Rs, Rd            | 1   | 6    | rs rd      |             | 2                    |

Notes: None

## A.2.6 ANDC (AND Control Register)

Assembler Format: ANDC #:8, CCR

Operation: (CCR) A (Immediate data) -> (CCR)

Description: Performs a logical AND operation between the immediate data and CCR, and loads the result to the CCR. All interrupts are not detected at completion of this instruction.

Operand Size: Byte

Condition Codes:

S\*: Same as the corresponding bit of the result.

## Operand Format and Number of Execution States:

## **Instruction Format**

| Addressing<br>Mode | Mnemonic | Operand<br>Format | 1st | Byte | 2nd Byte 3rd Byte | Exec.<br>4th Byte States |

|--------------------|----------|-------------------|-----|------|-------------------|--------------------------|

| Immediate          | ANDC     | #:8, CCR          | 0   | 6    | Imm               | 2                        |

Notes: None

#### A.2.7 BAND (Bit AND)

Assembler Format: BAND #:3, <EAd>

Operation: C A (<Bit number> of <Destination>) -> C

Description: Performs a logically AND operation between the C flag and a bit of destination operand, and loads the result into the C flag (Figure A-3). The bit number is specified by 3-bit immediate data. The destination operand is not affected by the BAND instruction.

Figure A-3. BAND Operation

Operand Size: Byte

Condition Codes:

I - H - N Z V C

S\*: C set if result is "1"; cleared otherwise.

#### **Instruction Format**

| Addressing<br>Mode | Mnemonio | Operand<br>Format | 1st | Byte | 2nd  | Byte | 3rd | Byte | 4th Byte | Exec.<br>States |

|--------------------|----------|-------------------|-----|------|------|------|-----|------|----------|-----------------|

| Register direct    | BAND     | #:3, Rd           | 7   | 6    | 0 Im | m rd |     |      |          | 2               |

| Register indirect  | BAND     | #:3, @Rd          | 7   | С    | 0 rd | 0    | 7   | 6    | 0 Imm 0  | 6               |

| Absolute address   | BAND     | #:3, @aaaa:8      | 7   | Е    | abs  |      | 7   | 6    | 0 Imm 0  | 6               |

Notes: "Addressing mode" above specifies effective address <EAd>.

## A.2.8 Bcc (Branch Conditionally)

Assembler Format: Bcc disp.

Operation: If cc is true then PC + disp -> PC else go to next instruction.

**Description:** Branches to an address (branch destination) by adding displacement to the PC if the condition specified in the cc field is true; executes the next instruction otherwise. Displacement is 7-bit signed data, while the PC points to the next instruction address. Accordingly, the branch destination is within the range of -126 bytes to +128 bytes from Bcc.

Table A-1 lists condition codes and their mnemonics.

Table A-1. Conditions for Bcc

| Mnen | non-                       |      | Conditional                                                        | Signed Condition      |

|------|----------------------------|------|--------------------------------------------------------------------|-----------------------|

| ic   | Condition                  | Code | Expression                                                         | Code                  |

| T    | True (BRA)                 | 0000 | 1                                                                  |                       |

| F    | False (BRN)                | 0001 | 0                                                                  |                       |

| HI   | High                       | 0010 | ~C·~Z [~(C + Z)]                                                   | x > y (Unsigned)      |

| LS   | Lower or same              | 0011 | C + Z                                                              | $x \le y$ (Unsigned)  |

| CC   | Carry Clear (High or Same) | 0100 | ~C                                                                 | $x \ge y$ (Unsigned)  |

| CS   | Carry Set (Low)            | 0101 | С                                                                  | x < y (Unsigned)      |

| NE   | Not Equal                  | 0110 | ~Z                                                                 | x≠y (Unsigned/Signed) |

| EQ   | Equal                      | 0111 | Z                                                                  | x=y (Unsigned/Signed) |

| VC   | Overflow Clear             | 1000 | ~V                                                                 |                       |

| VS   | Overflow Set               | 1001 | V                                                                  |                       |

| PL   | Plus                       | 1010 | ~N                                                                 |                       |

| MI   | Minus                      | 1011 | N                                                                  |                       |

| GE   | Greater Than or Equal      | 1100 | N·V + ~N·~V<br>[~(N ++ V)]                                         | $x \ge y$ (Signed)    |

| LT   | Less Than                  | 1101 | $N \sim V + \sim N \cdot V [N ++ V]$                               | x < y (Signed)        |

| GT   | Greater Than               | 1110 | $N \cdot V \sim Z + \sim N \sim V \cdot Z$ $[\sim (Z + (N ++ V))]$ | x > y (Signed)        |

| LE   | Less Than or Equal         | 1111 | $Z + N \sim V + \sim N \cdot V$ $[Z + (N ++ V)]$                   | $x \le y$ (Signed)    |

|      |                            |      |                                                                    |                       |

Operand Size: None

## Condition Codes:

## Operand Format and Number of Execution States:

#### Instruction Format

| Mnemonic  | Operand<br>Format                                                                 | 1st                                                                                                                                                                                         | Byte                                                                                                                                                                                                                                                  | 2nd Byte 3rd Byte 4th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Exec.<br>Byte States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BT (BRA)  | disp                                                                              | 4                                                                                                                                                                                           | 0                                                                                                                                                                                                                                                     | disp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| BF (BRN)  | disp                                                                              | 4                                                                                                                                                                                           | 1                                                                                                                                                                                                                                                     | disp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |